### Lab 2 Part 1 -

**Create** a Verilog hardware description for the 7408 AND gate. When this is written, do a SYNTAX check by compiling this file. IF you get errors, go back and fix them. Usually it's best to fix the first error and re-compile. When you get a successful compilation, you then assign pins to the two inputs and one output. (See the ISE tutorial in this lab manual) You assign the pins according to function. Inputs of the gates should be assigned a switch, and the output should be assigned an LED. Deciding which switch and LED is up to you!

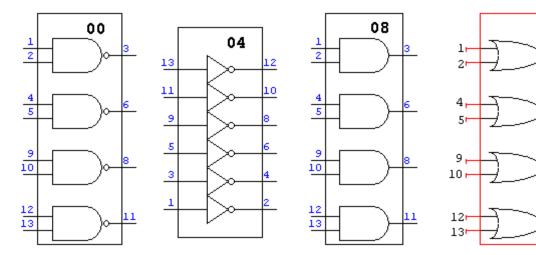

Once the pin assignment is done, you move on to downloading your design to the XILINX\_64 circuit board. (Again, see the ISE tutorial in this lab manual) If that is done successfully, you can now TEST your circuit against the truth table you have prepared for lab. Write down your OBSERVED results next to your PREDICTED results. Create 3 more files (one file for each remaining gates) using structural Verilog programming for the 74LS00, 74LS04, and 74LS32. After you have done this, compile, download, and test each of them as you did the 7408 AND gate. Report your results.

Remember we are only mimicking the function of the 7400 Series TTL gates using Verilog and our Programmable Logic.

Verilog has built in primitives that can be used to describe a circuit using **structural** modeling. The following primitives are for combinational logic circuits.

and, nand, or, nor, xor, xnor, not, buf.

Use four of these primitives to describe four 7400 Series TTL integrated circuits (ICs):

Remember there are 4 independent gates in each integrated circuit (7400 NAND, 7408 AND, 7432 OR) and 6 independent gates in the 7404 (NOT IC).

#### Lab 2 Part 1 (continued)

The following Verilog has been written for you. Type these descriptions in the ISE editor, and compile, download, and test to be sure they follow the truth table correctly. In your lab report, make the truth tables and logic diagrams for each Verilog Module.

# (Note: these modules do not include the output inverter needed for the ACTIVE LOW drive for the LEDs – see notes from lecture)

| modul                                                                     | <pre>e andgate(in1,in2,out);     input in1,in2;     output out;</pre> | modul                                                                       | <pre>e notgate(in1,out); input in1; output out;</pre> |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------|

|                                                                           | wire in1, in2, out;                                                   |                                                                             | wire in1, out;                                        |

|                                                                           | and gl(out,in1,in2);                                                  |                                                                             | <pre>not g1(out,in1);</pre>                           |

| endmodule                                                                 |                                                                       | endmodule                                                                   |                                                       |

|                                                                           |                                                                       |                                                                             |                                                       |

| <pre>module orgate(in1,in2,out);     input in1,in2;     output out;</pre> |                                                                       | <pre>module nandgate(in1,in2,out);     input in1,in2;     output out;</pre> |                                                       |

|                                                                           | wire in1, in2, out;                                                   |                                                                             | <pre>wire in1, in2, out;</pre>                        |

|                                                                           | or gl(out,in1,in2);                                                   |                                                                             | <pre>nand g1(out,in1,in2);</pre>                      |

| endmodule                                                                 |                                                                       | endmodule                                                                   |                                                       |

|                                                                           |                                                                       |                                                                             |                                                       |

\* \*

Create a single module instead of four independent modules. This module should have 2 inputs and 4 outputs. There is an output for each function.

# Lab 2 PART 2

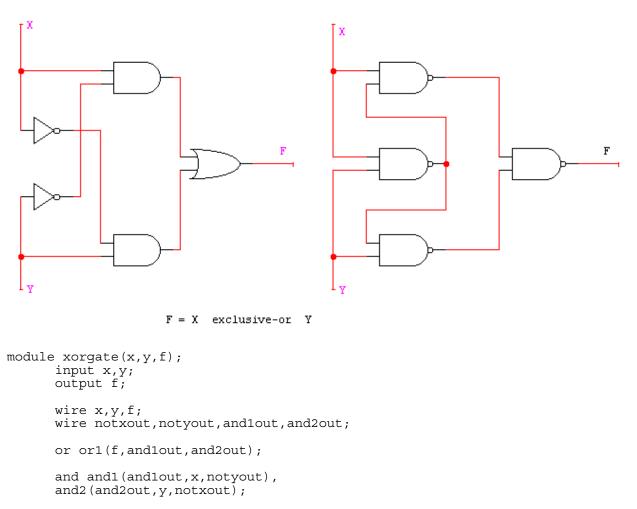

Each circuit below is a two input EXCLUSIVE-OR gate. Recall that an EXCLUSIVE-OR has a high output if one or the other inputs are high. Write a structural model to implement this function. You can write two description programs, one for each logic diagram, or combine them into one module. Compile, download, and test each circuit. In your report, show that each circuit satisfies the truth table for an EXCLUSIVE-OR function.

# Re-draw each circuit for your lab report with the proper names of each internal node and inputs/outputs (I/O).

not notx(notxout,x),

noty(notyout,y);

endmodule

#### **QUESTION #1:**

Is there an easier way to write an EXCLUSIVE-OR function still using primitives and structural modeling? Explain in the conclusion portion of your report.

#### **QUESTION #2:**

If you really needed to use EXCLUSIVE-OR gates could you buy a 7400 Series TTL Integrated Circuit (IC)? If so, what is the TTL part number and explain and draw the pin out of the device.

## LAB 2 Part 3

Consider a circuit with 4 inputs A, B, C, and D and one output F. Input A shall be the most significant bit. Create a truth table to implement the equation below. Show all the work (Boolean Algebra) as part of the design to reduce the equation for F. Draw the logic diagram (with names of internal and external signals) for your final reduced equation. After completing your logic diagram, write the Verilog description using "**Structural Modeling**". Compile, download and test your design against the truth table you made from the original equation below.

# $\mathbf{F} = /((/C + /D) \cdot (/A + B + /D)) \leftarrow \text{(using standard AND OR NOT symbols)}$

Note: If you wrote the above equation in Verilog HDL using the "dataflow" modeling technique, the equation would look like this:

F = ~((~C | ~D) & (~A | B | ~D))

## LAB 2 Part 4

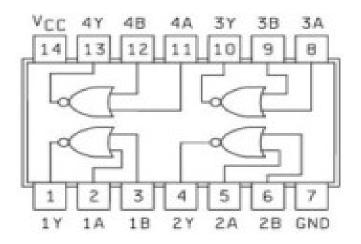

This exercise is to improve your method of reduction techniques. Use only the **four** integrated circuits (ICs) packages: the 7400 (NAND), 7404(NOT), 7408(AND) and 7432(OR), and **wire up your design that you created from the Truth Table**.

#### **Description:**

Consider a circuit with 4 inputs A, B, C, and D and two outputs F1 and F2. Input A shall be the most significant bit. Design a circuit to implement the given Truth Table. Show all the work (K-maps, Boolean Algebra, DeMorgan's) as part of the design to find the final equations for both F1 and F2. Also create the "**complete**" **schematic** diagram (and include in your lab report) for the circuit using the four (or less) integrated circuits (ICs). When you are happy with your design, wire it up on your white proto board.

Note: Both F1 and F2 must function at the SAME time, so your schematic diagram will have both outputs and shall be realized with both outputs functioning at the same time. (Hint: Share circuits from each function)

### Truth Table

| Inputs |   |   |   | Outputs |    |  |

|--------|---|---|---|---------|----|--|

| A      | в | С | D | F1      | F2 |  |

| 0      | 0 | 0 | 0 | 0       | 1  |  |

| 0      | 0 | 0 | 1 | 1       | 1  |  |

| 0      | 0 | 1 | 0 | 0       | 1  |  |

| 0      | 0 | 1 | 1 | 0       | 1  |  |

| 0<br>0 | 1 | 0 | 0 | 0       | 0  |  |

|        | 1 | 0 | 1 | 1       | 1  |  |

| 0      | 1 | 1 | 0 | 0       | 1  |  |

| 0      | 1 | 1 | 1 | 0       | 0  |  |

| 1      | 0 | 0 | 0 | 1       | 0  |  |

| 1      | 0 | 0 | 1 | 1       | 1  |  |

| 1      | 0 | 1 | 0 | 0       | 1  |  |

| 1      | 0 | 1 | 1 | 0       | 1  |  |

| 1      | 1 | 0 | 0 | 0       | 0  |  |

| 1      | 1 | 0 | 1 | 1       | 1  |  |

| 1      | 1 | 1 | 0 | 0       | 1  |  |

| 1      | 1 | 1 | 1 | 0       | 0  |  |

Here is some information about the 7400 Series TTL Integrated Circuits:

### Dot near pin 1 or Notch at top center

Top View of a 14 pin 74xx device Dual In-Line Package (DIP)

3

6

8

-

11